## 14:332:231 DIGITAL LOGIC DESIGN

Ivan Marsic, Rutgers University **Electrical & Computer Engineering** Fall 2013

Lecture #23: Verilog Structural and Behavioral Design

# Hardware Description Languages

🗕 [ Recall from Lecture #22 ] 🕳

- Basic idea:

- Language constructs describe circuits with two basic forms:

- Structural descriptions: connections of components (gates & flip-flops). Nearly one-to-one correspondence with schematic diagram (circuit structure).

- Behavioral descriptions: use statements (assignments and tests of logical conditions) to describe the relationships between inputs and outputs (circuit function)

#### "Structural" example:

```

Decoder(output x0, x1, x2, x3; inputs a, b)

wire a_L, b_L;

inv(b_L, b);

inv(a_L, a);

and(x0, a_L, b_L);

and(x1, a_L, b);

and(x2, a, b_L);

and(x3, a, b);

```

#### "Behavioral" example:

```

Decoder(output x0, x1, x2, x3; inputs a, b)

case [a b]

00: [x0 x1 x2 x3] = 0x1;

01: [x0 x1 x2 x3] = 0x2;

10: [x0 x1 x2 x3] = 0x4;

11: [x0 \ x1 \ x2 \ x3] = 0x8;

endcase:

```

### Verilog Concurrent Statements

- Concurrent statements specify digital logic operation, from which a realization is synthesized; 3 common types:

- 1. Instance statement

- Instantiates a module, used in structural descriptions

- Similar to a constructor call in OO languages (C++, Java, ...)

- 2. Continuous assignment statement

- For behavioral descriptions of combinational circuits

- 3. al ways blocks (non-continuous assignments)

- For behavioral descriptions of synchronous sequential circuits

- Concurrent statements "execute" simultaneously and continuously

- Modeling the continuous operation of hardware where connected elements affect each other continuously, not just at particular, ordered time steps

3 of 29

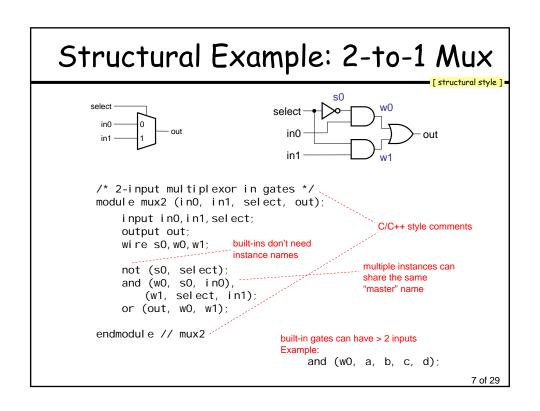

## Verilog Built-in Gates

[structural style]

Built-in gate names are reserved words

and, nand, or, nor ~ any number of inputs per gate xor, xnor

buf = 1-input noninverting buffer

not = inverter

bufif0, bufif1 = 1-input buffer w/ tri-state out

notif0, notif1 = inverter w/ tri-state outputs

Other predefined components include AND-OR-INVERT (sum-of-products) gates flip-flops, decoders, multiplexers, ...

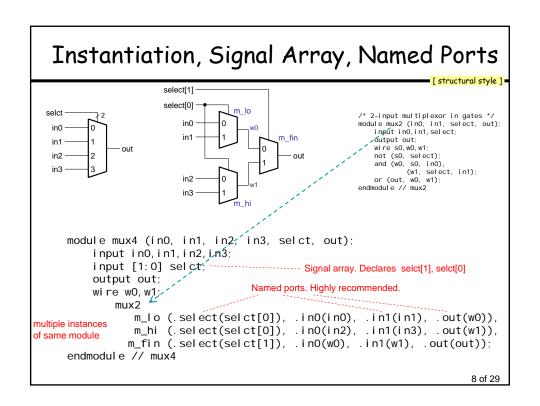

### Verilog Instance Statement

[structural style]

Two formats of instance statement:

component-name instance-identifier ( expr, expr, ..., expr );

component-name instance-identifier ( .port-name(expr), ..., ..., .port-name(expr), ..., ..., .port-name(expr) );

- Multiple instances of the same component/module distinguished by unique names ("instance-identifier")

- The 1<sup>st</sup> format depends on the order in which port names appear in the original component/module definition

- Expressions listed in the same order as ports to which they connect

- For built-in gates, the defined port order is (output, input, inpu

- · The order among the multiple inputs doesn't matter

- For built-in three-state buffers and inverters, the defined order is (output, data-input, enable-input)

- The 2<sup>nd</sup> format explicitly names the ports

- Recommended because it helps avoid mistakes in coding

5 of 29

### Structural Model - XOR example

module name port list module xor\_gate ( out, a, b ); i nput a, b; \_\_\_\_\_ port declarations output out; wi re a\_L, b\_L, t1, t2; internal signal declarations instance statements: not invA (a\_L, a); not invB (b\_L, b); out = a ⊕ b built-in gates and and1 (t1, a, b\_L); and and2 (t2, b, a\_L); or or1 (out, t1, t2); endmodul e interconnections (note that output is first) instance name/identifier (each must be unique w/in the module) Notes: - The instantiated gates are not "executed". They are always active. XOR gate already exists as a built-in (only an example – no need to define it)

Undeclared variables are assumed to be wi res. Don't let this happen to you!

#### Parameterized Module

[structural style ]

- Parameterize structural modules to handle inputs and outputs of any width

- Example: 3-input majority function

```

- Outputs "1" if at least two inputs are "1"

OUT = I0·I1 + I1·I2 + I2·I0

module Maj (OUT, I0, I1, I2);

parameter WID = 1;

input [WID-1:0] I0, I1, I2;

output [WID-1:0] OUT;

assign OUT = I0 & I1 | I1 & I2 | I2 & I0;

endmodule;

```

- When Maj module instantiated using regular syntax, the parameter WI D takes on default value 1

- Instance statement allows parameter substitution using #

- Example: X, Y, Z are 8-bit input vectors, the 8-bit majority function:

```

Maj #(8) U1 ( .OUT(W), .IO(X), .I1(Y), .I2(Z) );

```

9 of 29

## Simple Behavioral Model

modul e and\_gate (out, in1, in2);

input in1, in2;

output out;

"continuous assignment"

[assign out = in1 & in2;]

endmodul e

\* aND | = OR |

\* = XOR

\* continuous assignment"

connects out to be the AND of in1 and in2

- Shorthand for explicit instantiation of AND gate (in this case).

- The assignment happens continuously (modeling the continuous operation of hardware); therefore, any change on the right-hand-side (RHS) signals is reflected immediately on the output port (except for the small delay associated with the implementation of the "&" operation).

- Different from assignment in C that takes place when the program counter reaches that place in the program.

#### Continuous Assignment Statements

[ behavioral style ]

- assi gn net-name = expression;

- assi gn net-name[bit-indx] = expression;

- assi gn net-name[msb:lsb] = expression;

- assi gn net-concatenation = expression;

- Continuous-assignment statements are evaluated continuously (because hardware elements affect each other continuously, not just at particular, ordered time steps)

- The order of continuous assignment statements in a module doesn't matter

- Continuous-assignment statement is unconditional, but different values can be assigned using the conditional operator (?:)

# Continuous Assignment Examples

```

assign R = X | (Y & -Z);

assign r = &X;

assign R = (a == 1'b0) ? X : Y;

assign P = 8'hff;

assign P = X * Y;

arithmetic operators (use with care!)

assign P[7:0] = {4{X[3]}, X[3:0]};

assign Y = A << 2;</li>

bit shift operator

assign Y = {A[1], A[0], 1'b0};

assign Y = quivalent bit shift

```

# Non-continuous Assignments

al ways blocks and procedural code optional sensitivity list

Syntax of Verilog always blocks

- al ways @ (signal-name or ... or signal-name)

procedural-statement

- al ways procedural-statement

- al ways procedural-statement

- procedural-statement

- procedural-statement

- procedural-statement

- procedural-statement

- procedural-statement

- procedural-statement

- procedural-statement

- procedural-statement

- Procedural statements in an al ways block execute sequentially, as in software program

- However, always blocks execute concurrently with other concurrent statements in the module

- Note: assi gn statements must be used outside al ways statements; both are evaluated concurrently

## Procedural Sensitivity Lists

[ behavioral style ] =

- The execution of a statements within a procedure can be controlled using an event-control sensitivity list

- An al ways procedure must re-evaluate the outputs whenever an "input" changes value

- An "input" is any signal used to determine the value of assignments

- Procedures automatically become active at time zero

- Execution of statements is delayed until a change occurs on a signal in the "sensitivity list"

```

al ways @ ( <edge> <signal> or <edge> <signal> )

```

- <edge> may be posedge (positive) or negedge (negative)

- If no edge is specified, then any transition is used

- Sensitivity to multiple signals is specified using an "or" separated list

15 of 29

# al ways Block Example (1)

[ bahavianal style ]

- Sensitivity list signals @(...) determine when the al ways block executes

- The block is initially suspended and starts executing when any signal in the sensitivity list changes its value

- This continues until the block executes without any sensitivity-list signal changing its value

```

modul e and_or_gate (out, in1, in2, in3);

input in1, in2, in3;

output out;

reg out;

keyword

al ways (in1 or in3)

begin

out = (†n1 & in2) | in3;

end

endmodul e

"begin-end block" brackets multiple procedural statements (not necessary in this example)

```

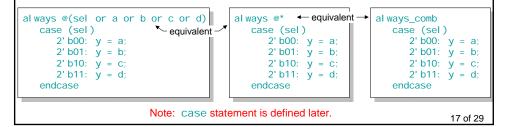

#### A Combinational Logic Sensitivity

[ behavioral style ]

- Verilog features a "wildcard" token to indicate a combinational logic sensitivity list

- The @\* token is a time control which indicates that the control is automatically sensitive to any change on any "input" to the statement or group-of-statements that follows

- An "input" is any signal whose value is read by the statement or statement group

- SystemVerilog introduced al ways\_comb for modeling combinational logic

- The simulator infers the sensitivity list to be all variables from the contained statements

# Verilog Procedural Statements

[behavioral style]

- Blocking assignment: variable-name = expression;

- Evaluates the expression immediately and assigns to variable

- Nonblocking assignment: variable-name <= expression;</p>

- Evaluates the expression immediately but does NOT assign to variable until an infinitesimal delay after the all ways block has completed execution

- begin-end block

- Encloses a list of procedural statements that execute sequentially

- if statement

- A condition (logical expression) is tested; if true the enclosed statement is executed

- case statement

- A "selection expression" followed by a list of "choices" and corresponding procedural statements

- Looping statements: for, while, repeat

- Execute the enclosed procedural statements for a given number of iterations

#### Blocking vs. Nonblocking Statements

[ behavioral style ]

#### Blocking assignment:

*variable-name = expression;*

- "immediate assignment" or within a specifiable delay

- Evaluates the expression immediately and assigns to variable

- Use blocking assignments to create combinational logic

- Nonblocking assignment:

variable-name <= expression;

- "nonblocking and slightly deferred assignment" or "late assignment"

- Evaluates the expression immediately but does NOT assign to variable until an infinitesimal delay after the al ways block has completed execution

- Use nonblocking assignments to create sequential logic

19 of 29

## al ways Block Example (2)

[ behavioral style ]

- Sensitivity list signals @(...) determine when the al ways block executes

- For example, the flip-flop includes only cl k in the sensitivity list

- Flip-flop remembers its old value of q until the next rising edge of the cl k, even if d changes in the interim

- In contrast, continuous assignment statements (assi gn) are reevaluated anytime any of the inputs on the right hand side changes therefore, such code necessarily describes combinational logic

- SystemVerilog introduced al ways\_ff, al ways\_l atch, and al ways\_comb (seen above) to imply flip-flops, latches, or combinational logic

- This reduces the risk of common errors

#### if statement

[ behavioral style ]

- A condition (logical expression) is tested; if true the enclosed procedural statement is executed

- Nested if-else example:

```

module mux4 (in0, in1, in2, in3, select, out);

input in0, in1, in2, in3;

input [1:0] select;

output out;

reg out;

keyword

al ways @ (in0 in1 in2 in3 select)

if (select == 2'b00) out=in0;

else if (select == 2'b01) out=in1;

else if (select == 2'b10) out=in2;

else out=in3;

endmodule // mux4

```

Nested if structure leads to "priority logic" structure, with different delays for different inputs (i n3 to out delay > than i n0 to out delay). case statement treats all inputs the same ...

21 of 29

#### case statement

[ behavioral style ]

- Evaluates the "selection expression," finds the first "choice" that matches the expression's value and executes the corresponding procedural statement

- case statement example:

```

module mux4 (in0, in1, in2, in3, select, out);

input in0,in1,in2,in3;

Recall that we could use a

input [1:0] select;

"wildcard" token * to indicate a

output out;

combinational logic sensitivity list

reg out;

or al ways_comb in SystemVerilog

al ways @*

always @ (in0 in1 in2 in3 select)

case (select)

case (sel ect)

2' b00: out=i n0;

endcase

2' b01: out=i n1;

The statement(s) corresponding

2' b10: out=i n2;

2' b11: out=i n3; The statements out to whichever constant matches

"select" get applied.

endmodule // mux4

22 of 29

```

11

## Incomplete case statement

[behavioral style]

- Listed choices may not be "all inclusive"—some possible values of the selection expression may be missing

- Incomplete case statement example:

```

module mux3 (in0, in1, in2, select, out);

input in0,in1,in2;

input [1:0] select;

output reg out;

If sel = 2' b11 = 3, mux will output the province

output the previous value!

always @ (in0 in1 in2 select)

-inferred an unwanted latch

case (select)

2' b00: out=i n0;

2' b01: out=i n1;

2' b10: out=i n2; <

Inferring an unwanted latch can be

prevented with a default statement:

endcase

default: out=1'bx;

endmodule // mux3

23 of 29

```

### for looping statement

[ bahavianal style 1 =

Syntax of a Verilog for statement:

for ( loop-index = first-expr, logical expression; loop-idx = next-expr ) procedural-statement

• for statement example — prime-number detector:

```

module Vprimebv (input [15:0] N, output reg F);

reg prime;

integer i;

keyword

al ways @ (N) begin

prime = 1; // initial value

if ( (N=1) || (N=2) ) prime = 1; // special cases

else if ((N % 2) == 0) prime = 0; // even, not prime

else for ( i = 3; i <= 255; i = i+2 ) i = loop-index

if ( (N % i) == 0) && (N != i) )

prime = 0; // set to 0 if N is divisible by any i

if (prime==i) F = 1; else F = 0;

end

endmodule // Vprimebv

```

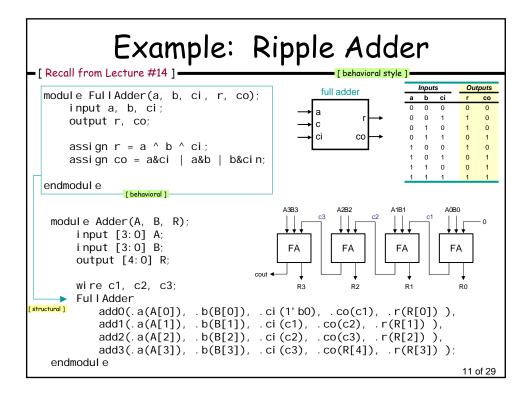

#### Behavioral vs. Structural

- Rule of thumb:

- Behavioral doesn't have sub-components

- Structural has sub-components:

- Instantiated Modules

- Instantiated Gates

- Instantiated Primitives

- Most levels are mixed

25 of 29

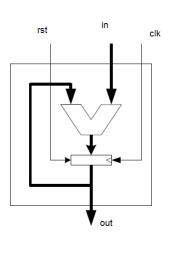

# Behavioral Example

- Behavioral only

- No instantiations

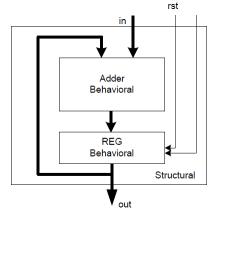

### Behavioral and Structural

- Behavioral:

- Adder function

- Register function

- Structural:

- Top module

- Two instantiations

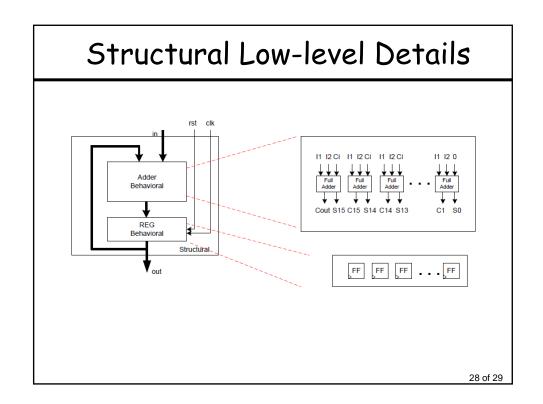

## Design Strategy

- Generally, complex systems are designed hierarchically

- The overall system is described structurally by instantiating its major components ("subsystems")

- Each subsystem is described structurally from its building blocks ...

- Continued recursively until pieces are simple enough to describe behaviorally

- Recommended to avoid (at least minimize) mixing structural and behavioral descriptions within a single module