# A High-Slew Rate SiGe BiCMOS Operational Amplifier for Operation Down to Deep Cryogenic Temperatures

Ramkumar Krishivasan, Yuan Lu, Laleh Najafizadeh, Chendong Zhu, John D. Cressler, Suheng Chen<sup>1</sup>, Chandradevi Ulaganathan<sup>1</sup>, and Benjamin J. Blalock<sup>1</sup>

School of Electrical and Computer Engineering

777 Atlantic Drive, N.W., Georgia Institute of Technology, Atlanta, GA, 30332-0250, USA

<sup>1</sup>University of Tennessee, Knoxville, TN 37996-2100, USA

**Abstract**— We investigate, for the first time, the design and implementation of a high-slew rate op-amp in SiGe BiCMOS technology capable of operation across very wide temperature ranges, and down to deep cryogenic temperatures. We achieve the first monolithic op-amp (for any material system) capable of operating reliably down to 4.3 K. Two variants of the SiGe BiCMOS op-amp were implemented using alternative biasing schemes, and the effects of temperature on these biasing schemes, and their impact on the overall op-amp performance, is investigated.

## I. INTRODUCTION

Operational amplifiers (op-amps) represent a ubiquitous and essential analog building block that finds application in a wide variety of high-performance precision analog circuits such as switched-capacitor filters, analog-to-digital converters, and precision sensors. Recently, there has been a growing interest in using such high-performance analog circuits for niche applications such as "extreme environment" electronics, and in particular for electronics capable of operating down to deep-cryogenic temperatures, as might, for instance, be encountered on the Moon (+120 °C to -180 °C and even down to -230 °C) [1].

The key device parameters of bandgap-engineered silicon-germanium (SiGe) heterojunction bipolar transistors (HBTs), such the transconductance ( $g_m$ ), current gain ( $\beta$ ), and Early voltage ( $V_A$ ), that are critical to op-amp performance are favorably impacted by cooling [2]. Thus, analog building blocks such as op-amps designed using a combination of scaled Si CMOS and SiGe HBTs could potentially offer an optimal solution for such cryogenic applications. Although the key device parameters of well-designed SiGe HBTs show remarkable improvement down to cryogenic temperatures, it remains to be demonstrated that this device-level performance in fact translates to superior circuit performance at low temperatures. NASA's upcoming lunar missions present a unique venue for practicing low temperature electronics in the SiGe material system. The envisioned lunar robotic electronics systems will be subjected to very large temperature variations (> 300 °C), and are cyclic in nature. Traditionally, the on-board electronics are housed in a centralized "warm box," which shields them from dramatic temperature changes, thus maintaining a narrow temperature range required for their reliable operation. Such warm boxes, apart from being power hungry, bulky, and heavy, compromise the ability to realize distributed system architectures [1].

Because of its attractive cryogenic performance and inherent robustness to ionizing radiation, SiGe-based mixed-signal electronic systems could potentially be deployed outside the space-craft warm box in so-called remote electronics units (REUs), for

needed sensing and data acquisition functions. Realization of key circuit blocks such as voltage and current references, op-amps, and ADCs in SiGe technology are a critical first step.

In this work we demonstrate a SiGe BiCMOS op-amp for such extreme temperature range lunar electronic systems. We achieve the first monolithic op-amp (for any material system) capable of operating reliably down to 4.3 K. The design methodology used in the present work is based on a circuit architecture described in [3]. The high-slew rate capability is achieved by using an auxiliary slew-buffer that enhances the output drive capability during slewing. Two variants of the SiGe BiCMOS op-amp were implemented using alternative biasing schemes and the effects of temperature on these schemes, and the overall performance of the op-amp, is carefully examined.

## II. DEVICE TECHNOLOGY AND CRYOGENIC OPERATION

This SiGe BiCMOS op-amp was fabricated in a commercial, deep and shallow-trench isolated SiGe HBT BiCMOS technology, which integrates 0.5  $\mu$ m, 3.3 V  $BV_{CEO}$ , 50 GHz  $f_T$ , 3.3 V  $BV_{CEO}$ , and 55 V  $V_A$  SiGe HBTs (at 300 K), together with 0.5  $\mu$ m, 3.3 V Si CMOS devices [4]. It supports a full suite of passive elements including metal-insulator-metal (MIM) capacitors and low  $T_C$  poly resistors. This is a five metal layer process (all aluminum) with a top thick aluminum layer that enables high- $Q$  spiral inductors.

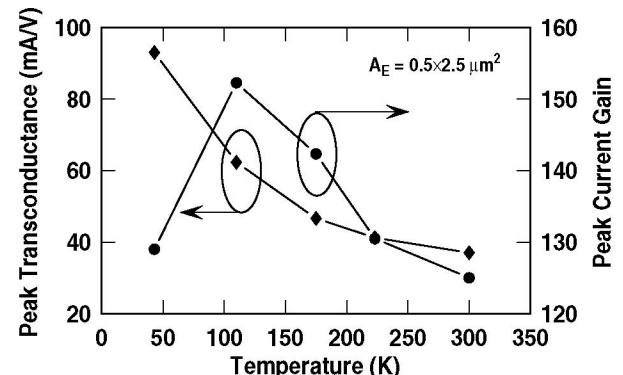

Fig. 1. Peak  $g_m$  and peak  $\beta$  versus temperature of the SiGe HBT with emitter area of  $0.5 \times 2.5 \mu\text{m}^2$ .

The SiGe HBTs from this technology generation show a strong monotonic increase in peak  $g_m$  with cooling (Fig. 1). In addition, with the base bandgap effects coupling strongly to the device equations in SiGe HBTs,  $\beta$  either increases or stays close

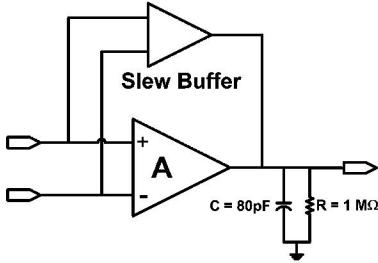

Fig. 2. The op-amp block diagram showing the core amplifier (A), the slew buffer, and a typical load condition.

to its room-temperature value down to deep cryogenic temperatures (Fig. 1). Although the increase in peak  $g_m$  should favorably translate into improved gain-bandwidth and slew rate performance in op-amps at low temperatures, this is highly dependent on the behavior of the bias current over temperature, as addressed below.

### III. CIRCUIT DESIGN

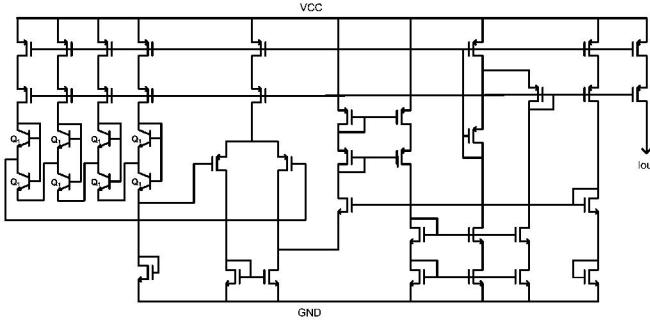

The block diagram of the SiGe BiCMOS slew-enhanced op-amp is shown in Fig. 2. The overall amplifier consists of an amplifier core, which provides all the small-signal amplifier gain, and the auxiliary slew-buffer, which comes into action when the input is slewing, thus enabling the fast slewing of the output under very large capacitive loads. The amplifier is designed to work off of a single power supply  $V_{cc}$  of 3.3 V. The unity-gain buffer configuration of the amplifier is obtained by connecting the output of the op-amp to the negative input.

#### A. Amplifier Core Design

The amplifier core was implemented using the conventional folded cascode topology [5]. The folded cascode architecture achieves a wider input common mode range (ICMR), higher gain, more stable control over gain-bandwidth (due to self-compensation), higher output impedance, and higher power supply rejection, than a two stage op-amp with active loads. SiGe HBTs were used in the input differential pair to exploit their large  $g_m$  and inherent enhancement with cooling, and their superior matching properties. Due to the large output resistance of the SiGe HBT, the dominant pole of the op-amp is at the output, and hence the small-signal gain-bandwidth product (GB) of the self-compensated op-amp (including the slew buffer) is given by,

$$GB = \frac{g_m}{C_L} \quad (1)$$

where  $g_m$  is the transconductance of a SiGe HBT in the input differential pair, and  $C_L$  is the load capacitance.

#### B. Slew-Enhancement Technique

There are several techniques available for slew-enhancement of conventional op-amps, each with differing trade-offs. The technique described in [6] achieves slew-enhancement by internally switching the output buffer to high-drive mode when the inputs are slewing. This technique, however, can not be easily extended to the amplifier cores in a folded cascode architecture, and has been reported to have large variations in quiescent current with varying temperature [3], and thus not suitable for

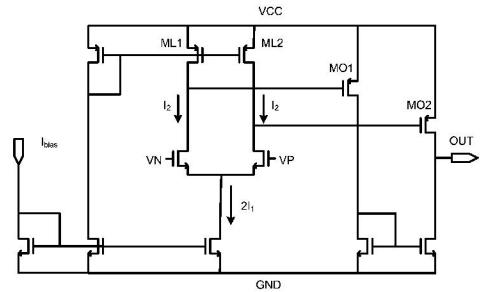

Fig. 3. Folded cascode amplifier core with bias block and SiGe HBT input stage.

Fig. 4. Slew buffer with load transistors biased in the linear region.

wide temperature range operation needed here. Another slew-enhancement technique employs an adaptive biasing scheme [7] where the bias current to the amplifier core is increased by a factor of the difference in the branch currents of the input differential pair. When the input slews, there is a large mismatch in the branch current, resulting in large core bias current, and thus providing a higher drive at the output. This technique suffers from high power dissipation in the amplifier core during transients.

The slew-enhancement used in the current design is achieved by using a slew buffer (Fig. 4) whose load transistors  $ML1$  and  $ML2$  are biased in the triode region. This condition is achieved by sizing  $ML1$  and  $ML2$  such that  $I_1 < I_2$ , where  $I_1$  is half the tail current and  $I_2$  is the saturation current in  $ML1$  and  $ML2$ . Thus, under small-signal conditions when the input terminals  $VP$  and  $VN$  are nearly equal, the gates of  $MO1$  and  $MO2$  (the output transistors) are pulled close to  $V_{cc}$ , turning them off. However, when the input is slewing, there is a large difference in the potentials of  $VP$  and  $VN$ , causing one of the load transistors to saturate, thereby pulling the gate terminal of the corresponding output transistor closer to ground potential. This turns on the output transistor very hard, causing it to deliver large currents to the output. Hence, during slewing the bias to the amplifier core is unaffected, which is clearly desirable. The threshold input differential voltage ( $V_{in,th}$ ) required for triggering the slew buffer is given by [3],

$$V_{in,th} = \alpha \sqrt{\frac{I_1}{\kappa}} \quad (2)$$

where  $\alpha$  is defined such that  $I_2 = (1 + \alpha)I_1$ , and  $\kappa$  is the MOS conductance parameter of the input transistors of the slew buffer.

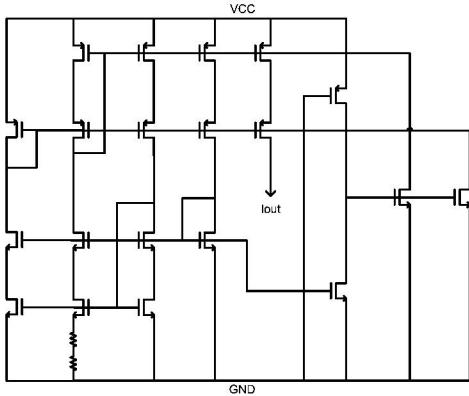

Fig. 5. Conventional wide-swing cascode current bias circuit with start-up.

Fig. 6. Weak-T current bias circuit with SiGe HBT PTAT chain and a transconductor (start-up circuit not shown).

### C. Biasing Schemes

The SiGe op-amp was implemented using two different bias schemes, each with a varying temperature response, for the output bias current. The first bias scheme utilizes a conventional wide-swing cascode bias circuit, as shown in Fig. 5 [8]. This bias scheme features a wide-swing bias current loop and a start-up circuit to avert the zero current bias condition. The efficacy of the start-up circuit was checked via simulations down to  $-55^{\circ}\text{C}$ , and worked well down to 4.3 K.

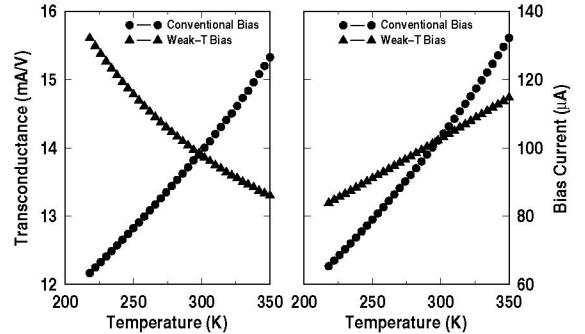

The second bias scheme, called "weak-T bias" here, is based on a resistor-free current reference that is designed to reduce overall analog performance variation over a wide temperature range (Fig. 6) [9]. The output bias current of this current source is given by,  $2m\mu C_{\text{ox}}U_T^2$  where  $m$  is a temperature independent scaling factor,  $\mu$  is the mobility ( $\propto T^{-1.5}$  for PMOS),  $C_{\text{ox}}$  is the oxide capacitance, and  $U_T$  is the thermal voltage. It is therefore expected that the resultant  $g_m$  of the SiGe HBT biased using this current source be proportional to  $\mu C_{\text{ox}}U_T$  ( $\propto T^{-0.5}$ ) and the corresponding slew rate be proportional to  $\mu C_{\text{ox}}U_T^2$  ( $\propto T^{+0.5}$ ). Thus the residual temperature dependence of these key parameters are rendered weak by this biasing scheme, ensuring reduced small-signal and large-signal performance variation over temperature. The simulated SiGe HBT  $g_m$  behavior over temperature for weak-T bias is in qualitative agreement with above analysis (Fig. 7). In addition, observe the opposite trends in  $g_m$  for these two different bias schemes.

Fig. 7. Simulated input SiGe HBT  $g_m$  of the two circuits versus temperature for the corresponding bias tail current.

## IV. MEASUREMENT RESULTS AND DISCUSSION

The *dc* and *ac* characterization was performed on the unity gain buffer configuration of the op-amp using a custom-designed cryogenic probe station capable of operating down to 4.3 K.

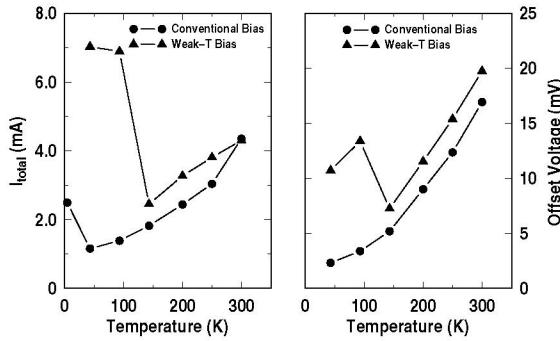

### A. DC Characteristics

The op-amps with either of the current sources drew a total bias current of 4.3 mA nominally at room temperature. The total bias current dropped monotonically with cooling in the conventional bias case and to 143 K in the weak-T based circuit (Fig. 8). There was, however, an anomalous increase in bias current below 143 K in the weak-T op-amp. The input-referred offset voltage tracked the temperature behavior of the bias current. The input-referred offset power for the op-amp can be approximated as [10],

$$V_{os}^2 = V_{os,\text{core}}^2 + V_{os,\text{slew}}^2, \quad (3)$$

where,

$$V_{os,\text{core}}^2 \simeq U_T^2 \left[ \frac{\Delta V_{TP}^2}{\left( \frac{V_{ov,p}}{2} \right)^2} + \frac{\Delta (W/L)_p^2}{(W/L)_p^2} + \frac{\Delta I_S^2}{I_S^2} \right], \quad (4)$$

and

$$V_{os,\text{slew}}^2 \simeq \Delta V_{TN}^2 + \left( \frac{V_{ov,N}}{2} \right)^2 \times \left[ \frac{\Delta V_{TP}^2}{\left( \frac{V_{ov,N}}{2} \right)^2} + \frac{\Delta (W/L)_p^2}{(W/L)_p^2} + \frac{\Delta (W/L)_N^2}{(W/L)_N^2} \right]. \quad (5)$$

Therefore, the offset contribution from the core amplifier is expected to drop naturally with cooling ( $\propto U_T^2 \propto T^2$ ) and with the decrease in bias current ( $\propto V_{ov} \propto I_{bias}^2$ ), and for the same reason the contribution from the slew buffer is expected to also drop with bias current. Thus, the overall offset decreases with temperature for both bias schemes, clearly good news. The higher offset voltage in op-amp with weak-T bias is possibly due to the additional current mismatches introduced by PTAT chain and the transconductor, and is still under investigation.

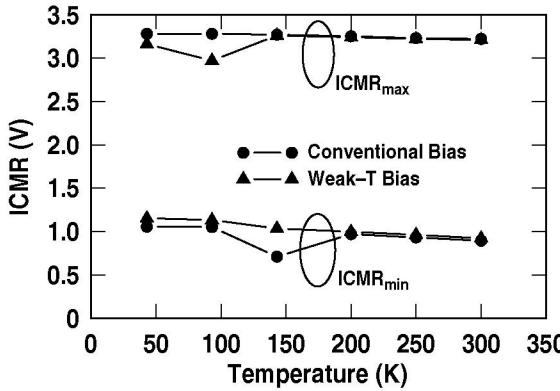

The ICMR of both variants of the SiGe op-amp remained fairly constant across temperature, as evidenced by Fig. 9. Closer examination of the  $\text{ICMR}_{\text{min}}$  does indicate a moderate increase attributable to the (expected) increase in the base-emitter turn-on voltage of the input differential pair with cooling.

Fig. 8. Measured total bias current and input-referred offset voltage versus temperature for the two circuits.

Fig. 9. Measured ICMR of the circuits as a function of temperature.

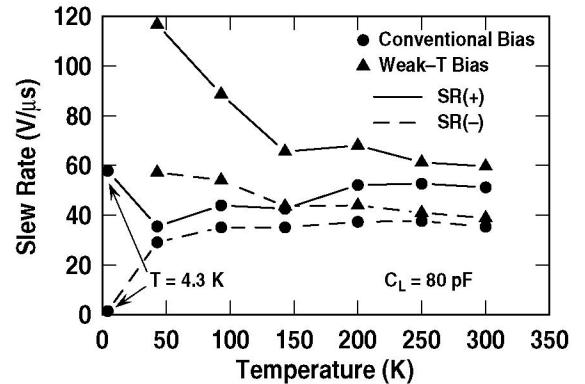

### B. Slew-Rate and Gain-Bandwidth

The op-amp with conventional bias displayed robust start-up down to 4.3 K, and had useful gain-bandwidth and appreciable slew rate at this temperature. To our knowledge, this is the first monolithic op-amp capable of operating at this low a temperature. The op-amp with weak-T bias showed a moderate increase in both positive and negative slew rates down to 143 K and further down in temperature a dramatic increase was observed in slew rate, which can be ascribed to the bias current behavior at these temperatures. The op-amp with conventional bias, on the other hand, showed only a moderate decrease in both the slew rates not readily explained using the bias current decrease. This slew rate behavior suggests that the slew-buffer effectively decouples the output slewing from the tail bias currents, and thus making it a weak function of temperature, a desirable attribute.

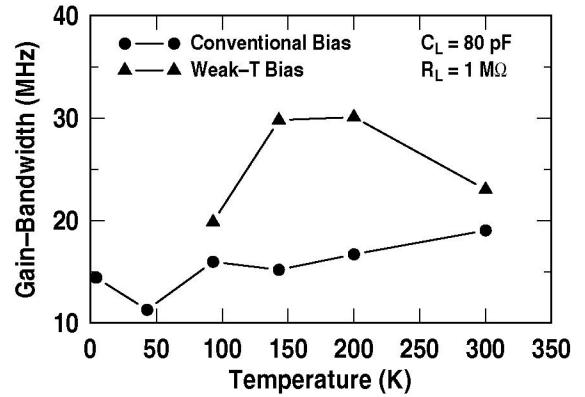

The small-signal gain-bandwidth is still tied intimately to the input transconductance of the op-amp. This observation was confirmed qualitatively by the comparing the simulated  $g_m$  of the input SiGe HBTs (Fig. 7) with the measured gain-bandwidth of the two circuits (Fig. 11). While the gain-bandwidth of the op-amp with weak-T bias increases with cooling down to 143 K, the gain-bandwidth of the conventional bias op-amp degrades steadily with cooling.

### V. SUMMARY

We have designed and implemented a SiGe BiCMOS op-amp capable of operating across a very wide temperature range, and

Fig. 10. The positive and negative slew rates of the circuits across temperature.

Fig. 11. Gain-bandwidth of the SiGe op-amps versus temperature.

down to temperatures as low as 4.3 K. We conclude that SiGe technology offers an ideal approach for developing a wide variety of analog and mixed-signal building blocks for emerging extreme environment electronics applications.

### ACKNOWLEDGMENT

This work was supported by NASA, under grant NNL05AA7C, and the Georgia Electronic Design Center at Georgia Tech. We are grateful for the support of C. Moore, M. Watson, M. Beatty, L. Nadeau of NASA, E. Kolawa of JPL, and the IBM SiGe development group, as well the many contributions of the SiGe ETDP team, including: M. Mojarradi, B. Blalock, W. Johnson, R. Garbos, R. Berger, F. Dai, G. Niu, L. Peltz, A. Mantooth, P. McCluskey, M. Alles, R. Reed, A. Joseph, C. Eckert, and J.D. Cressler.

### REFERENCES

- [1] J.D. Cressler, *Proc. IEEE*, 93, p. 1559, 2005.

- [2] J.D. Cressler *et al.*, *SiGe HBTs*, Norwood, MA: Artech House, 2003.

- [3] K. Nagaraj, *Electron. Lett.*, 25, p. 1304, 1989.

- [4] D.C. Ahlgren, *Tech. Dig. IEEE IEDM*, p. 859, 1996.

- [5] P.E. Allen *et al.*, *CMOS Analog Circuit Design*, New York, NY: Oxford University Press, 2002.

- [6] S.L. Wong *et al.*, *IEEE JSSC*, 21, p. 464, 1986.

- [7] M.G. Degrauwe *et al.*, *IEEE JSSC*, 17, p. 464, 1982.

- [8] D.A. Johns *et al.*, *Analog Integrated Circuit Design*, New York, NY: John Wiley & Sons, 1997.

- [9] S. Chen *et al.*, *submitted to WOLTE-7*, 2006.

- [10] P.R. Gray *et al.*, *Analysis and Design of Analog Integrated Circuits*, New York, NY: John Wiley & Sons, 2001.